查ICP網:全新的綜合網站備案信息查詢網

Copyright ? 2008-2028 www.mshuangcha.com [ 查icp] All Rights Reserved.

d觸發(fā)器的邏輯功能有哪些?D觸發(fā)器的邏輯功能:Qn+1=D。

D觸發(fā)器是一個具有記憶功能的,具有兩個穩(wěn)定狀態(tài)的信息存儲器件,是構成多種時序電路的最基本邏輯單元,也是數字邏輯電路中一種重要的單元電路。

在數字系統和計算機中有著廣泛的應用。觸發(fā)器具有兩個穩(wěn)定狀態(tài),即"0"和"1",在一定的外界信號作用下,可以從一個穩(wěn)定狀態(tài)翻轉到另一個穩(wěn)定狀態(tài)。

觸發(fā)器有集成觸發(fā)器和門電路組成的觸發(fā)器。觸發(fā)方式有電平觸發(fā)和邊沿觸發(fā)兩種,前者在CP(時鐘脈沖)=1時即可觸發(fā),后者多在CP的前沿(正跳變0→1)觸發(fā)。

D觸發(fā)器的次態(tài)取決于觸發(fā)前D端的狀態(tài),即次態(tài)=D。因此,它具有置0、置1兩種功能。

對于邊沿D觸發(fā)器,由于在CP=1期間電路具有維持阻塞作用,所以在CP=1期間,D端的數據狀態(tài)變化,不會影響觸發(fā)器的輸出狀態(tài)。

D觸發(fā)器應用很廣,可用做數字信號的寄存,移位寄存,分頻和波形發(fā)生器等等。

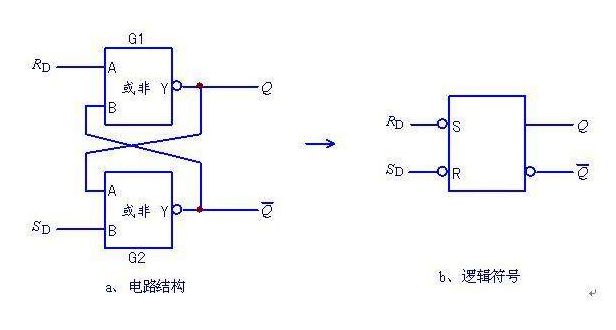

D觸發(fā)器由4個與非門組成,其中G1和G2構成基本RS觸發(fā)器。電平觸發(fā)的主從觸發(fā)器工作時,必須在正跳沿前加入輸入信號。如果在CP高電平期間輸入端出現干擾信號,那么就有可能使觸發(fā)器的狀態(tài)出錯。而邊沿觸發(fā)器允許在CP觸發(fā)沿來到前一瞬間加入輸入信號。

這樣,輸入端受干擾的時間大大縮短,受干擾的可能性就降低了。邊沿D觸發(fā)器也稱為維持-阻塞邊沿D觸發(fā)器。邊沿D觸發(fā)器可由兩個D觸發(fā)器串聯而成,但第一個D觸發(fā)器的CP需要用非門反向。